O Google Quantum AI revelou o Willow, um chip quântico de última geração que marca um grande avanço na computação quântica. O chip de 105 qubit atinge desempenho de qubit de última geração e a empresa relatou duas demonstrações importantes deste novo chip.

- Novos padrões de desempenho no benchmark Random Circuit Sampling (RCS). Em 2019, Sycamore demonstrou uma implementação de Random Circuit Sampling (RCS) alcançada em cerca de 3 minutos, um problema que um dos supercomputadores mais rápidos levaria quase 10.000 anos para resolver. Desde então, tanto os algoritmos clássicos quanto o hardware clássico dos supercomputadores melhoraram significativamente. Mas agora, em 2024, Willow concluiu o cálculo em menos de cinco minutos que levaria 10 dos maiores supercomputadores da atualidade.25 idade, ultrapassando em muito a idade do universo. Este resultado enfatiza a enorme vantagem computacional dos sistemas quânticos sobre os seus homólogos clássicos.

- Redução de erro exponencial: Willow demonstra como corrigir erros quânticos, alcançando taxas de erro reduzidas com grandes grades qubit. Pela primeira vez, o sistema está operando “abaixo do limite”, indicando a correção de erros que melhora o desempenho geral do sistema à medida que o número de qubits aumenta. Este marco, seguido há quase três décadas, é essencial para a construção de computadores quânticos poderosos e eficientes.

O Google fez várias melhorias com o chip Willow em relação ao seu antecessor Sycamore. Talvez o mais importante seja o fato de o Willow ser construído na nova fábrica de wafers do Google em Santa Bárbara, Califórnia. Sycamore foi construído no campus da Universidade da Califórnia em Santa Bárbara (UCSB). A empresa também aplicou melhorias no design do chip que proporcionaram uma melhoria cinco vezes maior em relação ao T1 o tempo paralelo, de 20 microssegundos para 100 microssegundos, a melhoria da confiabilidade do portão em quase duas metades e, claro, o aumento no número de qubits de 72 para 105.

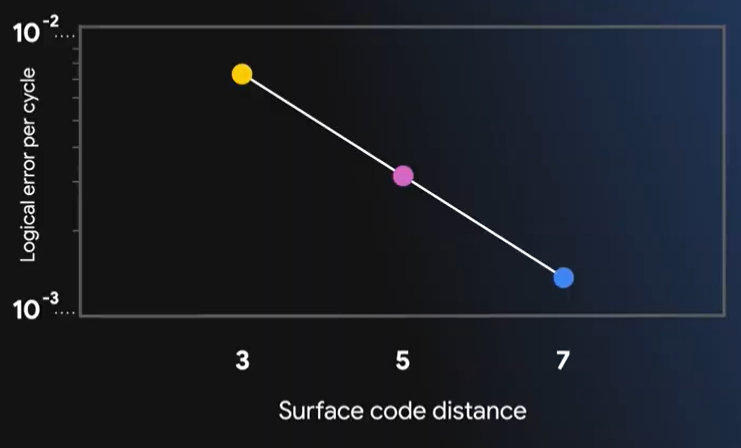

Em seu artigo técnico publicado na Nature, eles relatam a implementação de um código de correção de erros de superfície em grades 3×3, 5×5 e 7×7. Notavelmente, à medida que aumentaram o tamanho do código, observaram uma melhoria de quase duas vezes no desempenho da taxa de erros lógicos, conforme mostrado no gráfico abaixo.

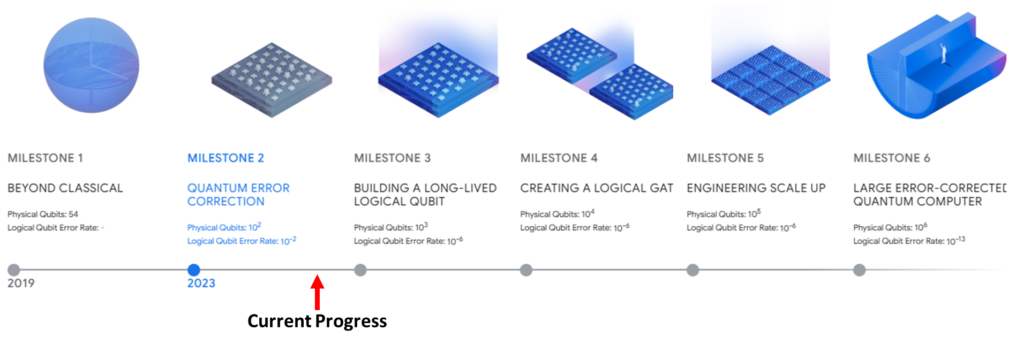

Embora alcançar uma taxa de erro razoável em torno de 10-3 seja muito bom, eles ainda têm um longo caminho a percorrer. Para colocar essas conquistas em perspectiva, se olharmos onde o Google está no roteiro, conforme mostrado abaixo, ainda há um longo caminho a percorrer. Eles criaram um qubit lógico com uma taxa de erro de 10-3 usando 101 qubits, com o próximo objetivo de atingir o Marco 3 com uma taxa de erro de qubit razoável de 10-6. Se a equipe do Google continuasse a expandir o design de qubit existente para tamanhos de grade maiores e continuasse na taxa de melhoria mostrada no gráfico acima, eles precisariam de 1.457 qubits físicos para atingir esses 10.-6 Uma taxa de erro razoável para o Marco 3. Mas é provável que a equipe continue a fazer melhorias adicionais no hardware ou no código de correção de erros para ser mais eficiente no alcance dessa meta para o Marco 3. Outro passo importante na criação de um sistema quântico tolerante a falhas O computador deverá demonstrar que eles podem usar o conjunto de portas globais representando uma porta não-Clifford como uma porta T.

Para mais detalhes, consulte o comunicado de imprensa e outras informações disponíveis no site do Google AI aqui.

9 de dezembro de 2024